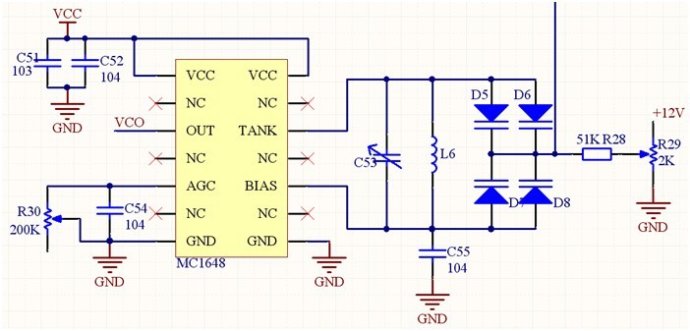

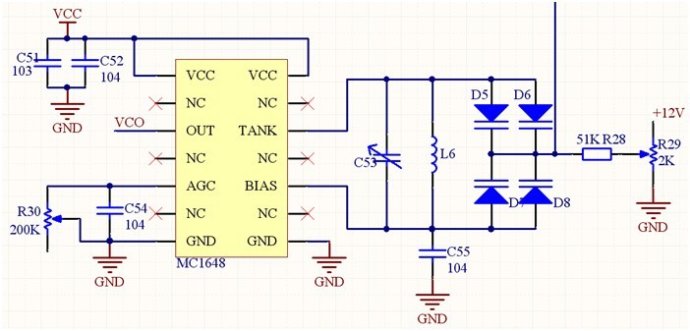

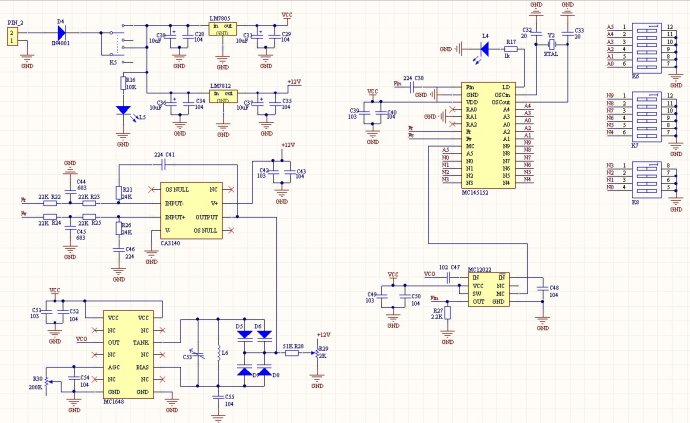

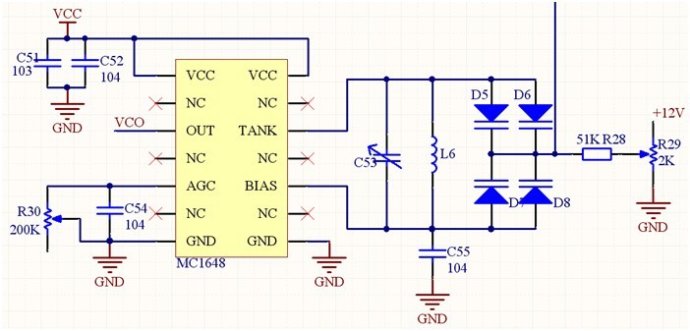

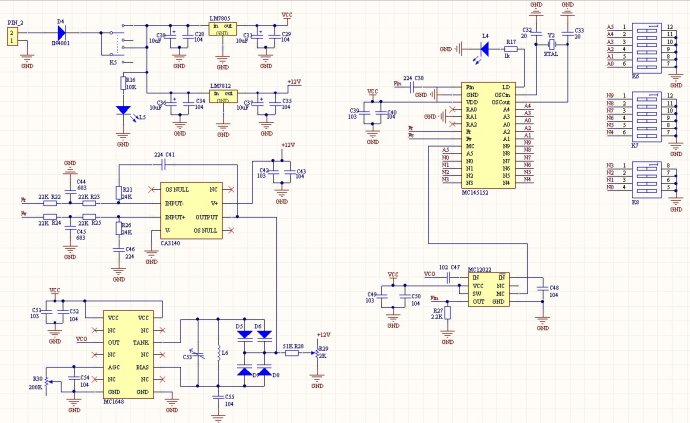

4.MC1648外圍電路(VCO)

C54����,C55采用獨石電容����,C53采用可調(diào)的瓷介電容(5pF~50pF)�����,其余電容采用普通瓷片電容即可�����。

R30是用于調(diào)整MC1648的OUT管腳輸出電平的幅度����,一般規(guī)律是:幅度越大��,失真越大�����;幅度越小���,失真越小����。由于OUT管腳輸出到MC12022����,為了讓MC12022能夠正常識別��,這里OUT管腳起碼要有幾百mV的幅度����。

D5�,D6,D7�,D8是變?nèi)荻O管,我使用了FV1043���,變?nèi)莘秶?pF~27Pf��?����?梢圆捎闷渌?nèi)荻O管代替�����,注意極性別接錯了(接錯也是可以振蕩的,但不能鎖定)��。它們采用頭對頭的連接方式,是對一些不穩(wěn)定因素起到對消的作用(具體作用不知道在哪里看過�,忘了)。而D5���,D6并聯(lián)��,D7�����,D8并聯(lián)����,是用于增大變?nèi)莸姆秶?��,因此可以多并?lián)幾個��。其他連接方式��,可以參考datasheet���。

L6是空心電感線圈(直徑3.5mm,圈數(shù):12�����,銅線直徑:0.6mm),記得采用包漆銅線繞制�。這里采用空心線圈有幾個原因:1.空心線圈的Q值比帶磁心的線圈高。2.手頭沒有性能明確的磁心(性能不明確的元件不用�,磁心材料種類太多了,不同材料應用的頻帶不同�,最好別亂用,況且高頻用的磁心真心不容易買到)���。

R28�,R29是為了測定某項參數(shù)而設定的���,實際工作的PLL��,需要把它們?nèi)サ簟?p>注意:與TANK和BIAS管腳連接的元器件�����,布線盡量短粗�。C51���,C52去耦電容也要盡可能靠近VCC����,這個對于其他芯片的外圍電路也一樣�。

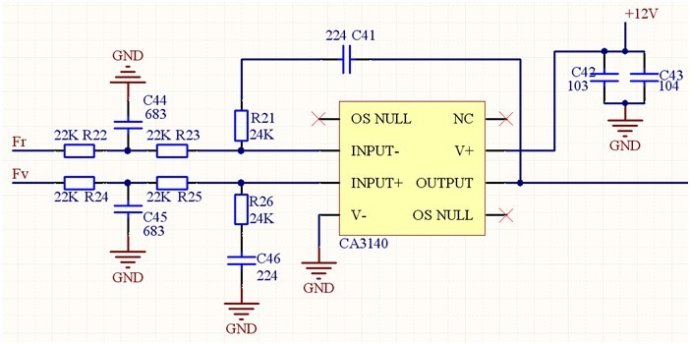

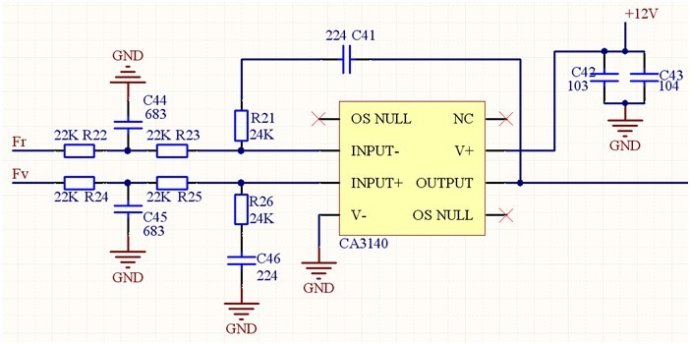

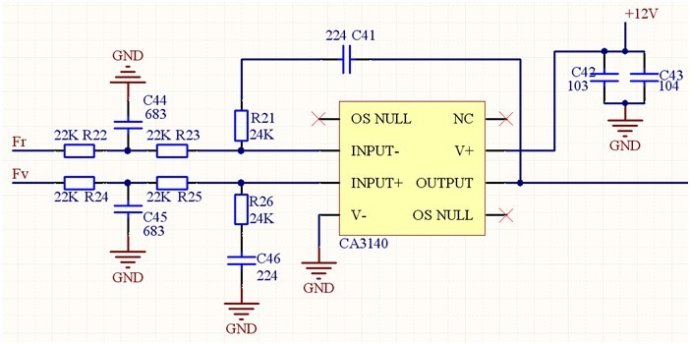

5.環(huán)路低通濾波器(LPF)

C42,C43去耦電容采用普通瓷片電容即可��,其余電容采用獨石電容��。

CA3140是一款性能優(yōu)異的運放��,這里的運放一定要精心挑選���,推薦兩款:CA3140���,MC33171。選擇這個運放有幾個很重要的性能要求:1.單電源供電�。2.GDB大于1MHZ。3.電壓轉(zhuǎn)換速率要快����。4.輸入阻抗大。滿足條件1�,2,3的運放�����,寥寥無幾,相當難找��。

整個PLL電路中��,環(huán)路濾波器的設計是關鍵所在����,影響整個PLL系統(tǒng)的特性,例如:鎖定速度����,相位噪聲,寄生頻率����,反饋的穩(wěn)定性。電阻電容的參數(shù)必須通過理論計算���,實際調(diào)整來確定����。

至于電路的調(diào)試過程�,LPF的參數(shù)計算����,下回分解吧����。吃飯去鳥~~~~

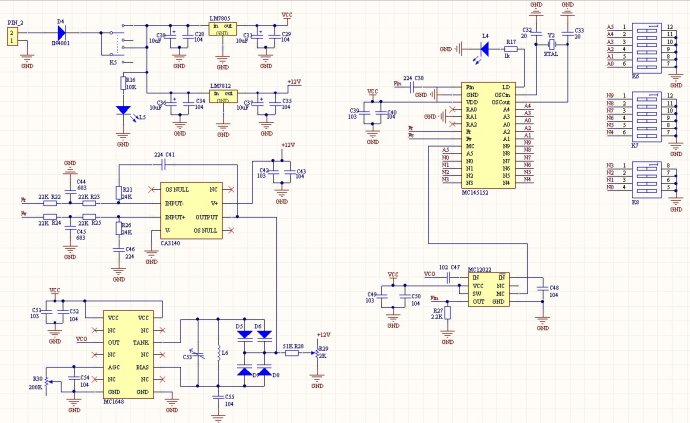

最后���,送上的原版電路圖截圖����。

評論