4 結論

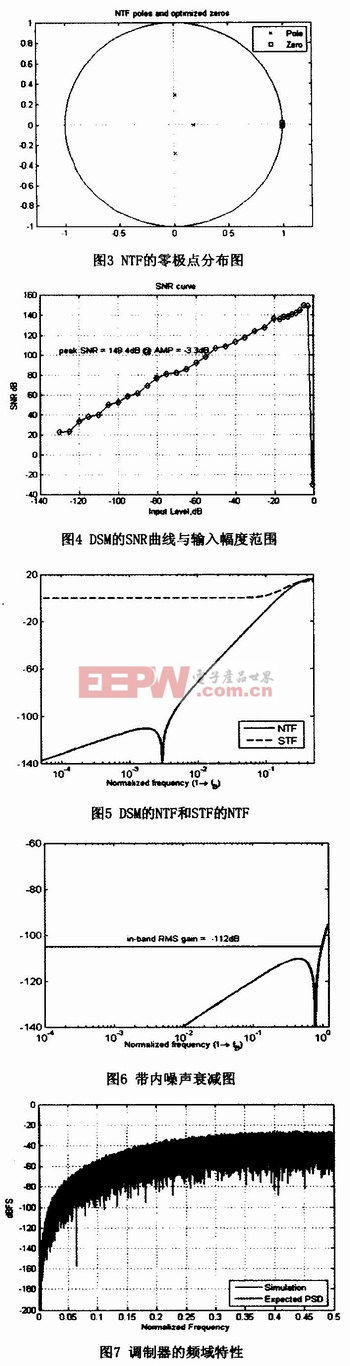

本文提出一個用在ADC中的16位的3階8級量化的三階單環(huán)Delta-sigma調制器�。為了提高電路性能,實現較高的SNR和DR,減少量化噪聲的影響�,在設計NTF時采用前饋方式和局部反饋的結構,并進行零點優(yōu)化���,通過這些方法優(yōu)化了輸出SNR�����,提高DR����,降低量化噪聲�,使得電路對于量化噪聲有較好的敏感度。根據仿真結果��,這個DSM的峰值SNR可以達到145dB以上�,在3階的系統(tǒng)和128的過采樣率下,達到相當高的SNR�,之后用Verilog語言對調制器各電路模塊進行建模與仿真。

評論